时域比较器深亚稳态研究及其在高精度ADC自校准中的应用

模数转换器(ADC)是模拟集成电路的核心问题之一,也是我国“卡脖子”的重大需求领域。近年来,逐次逼近(SAR)型ADC由于其高度数字化、功耗低、可并行等特点,在先进工艺下得到了长足的发展,并在高速领域逐步取得明显的优势。但受制于器件匹配,SAR ADC的高精度设计一直是个难题。而低功耗、低延迟、中高精度的ADC在传感器和自动控制系统中扮演着不可或缺的角色。本项研究借助先进工艺下的时间分辨率优势,提出了采用时域比较器的亚稳态特性进行自动校准的技术。为此,该项工作也首次给出了闭环时域比较器的亚稳态特性定量分析,并定义了亚稳态深度这一设计概念。

电子科技大学低功耗集成电路与系统研究所李强教授研究团队首先设计了一款基于压控振荡器(VCO)的闭环动态比较器,该比较器拥有电压、功耗与噪声等多个维度的自适应特性。利用随机过程理论对VCO比较器的噪声特性进行了理论分析,得出了闭环时域比较器行为的解析解,揭示出时域比较器独特的亚稳态特性。结合闭环时域比较器固有的“震荡周期数”这一设计空间(作者前期工作,发表于2019年第5期JSSC),提出了亚稳态深度这一概念并应用于自动误差探测与校准。论文提出了一种在模拟域进行自动电容匹配的设计方案,避免引入浮点计算等较为复杂的数字逻辑与处理,进一步节省芯片面积并降低系统功耗。

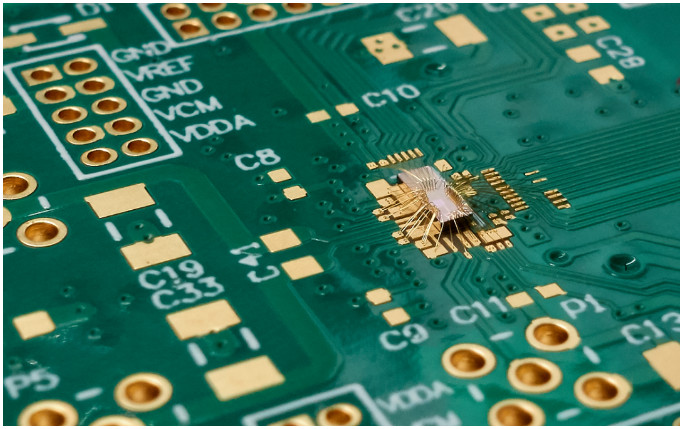

基于以上理论和设计方案,论文展示了一款14-bit 4-MS/s的SAR ADC,在40nm CMOS工艺流片并进行了验证。在2MS/s和4MS/s采样频率下分别取得78.7dB和76.6dB的峰值SNDR,以及超过93dB的无杂散动态范围(SFDR),整体功耗仅为94和157微瓦。该项工作证明了基于VCO的闭环时域量化除了具有多个维度的自适应特性,在高精度设计中也拥有较大的潜力,是未来超低功耗、中高精度ADC的可靠方案之一。

图1

论文链接: https://ieeexplore.ieee.org/document/8896893